网友您好, 请在下方输入框内输入要搜索的题目:

题目内容

(请给出正确答案)

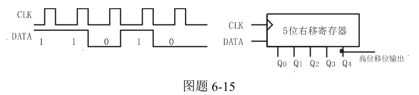

图题6-15所示的是5位右移寄存器与输入信号DATA、时钟CLK的波形图,若寄存器初始状态为00000,试画出寄存器输出Q4~Q0的波形图。

参考答案

更多 “ 图题6-15所示的是5位右移寄存器与输入信号DATA、时钟CLK的波形图,若寄存器初始状态为00000,试画出寄存器输出Q4~Q0的波形图。 ” 相关考题

考题

图题6-17所示的是8位右移寄存器74HC164与共阳数码管的连接图,其输入信号DATA、时钟CLK的波形图,若寄存器初始状态为0000000,试画出74HC164输出QF~QA的波形图,并说明数码管显示的数字是多少?

考题

图题6-18所示的是并入串出8位右移寄存器74HC165的连接图,以及输入信号CLKINH、移位/置数信号SH/与时钟CLK的波形图,若74HC165并入数据为11100101,试画出74HC165输出Y的波形图。

考题

填空题移位寄存器指令SHRB将DATA数值移入移位寄存器。梯形图中,EN为使能输入端,连接移位脉冲信号,每次使能有效时,整个移位寄存器移动()位。DATA为数据输入端,连接移入移位寄存器的二进制数值,执行指令时将该位的值当N值为正时移入寄存器S_BIT指定移位寄存器的最低位。

考题

填空题移位寄存器指令SHRB将DATA数值移入移位寄存器。梯形图中,N指定移位寄存器的长度,移位寄存器的最大长度为64位,N为正值表示(),输入数据(DATA)移入移位寄存器的最低位(S_BIT),并移出移位寄存器的最高位。

考题

填空题PLC通过(),将外部信号的状态读入并存储在输入映像寄存器内。

热门标签

最新试卷